Double Pinned Perpendicular-Magnetic-Tunnel-Junction Spin-Valve Providing Multi-level Resistance States | Scientific Reports

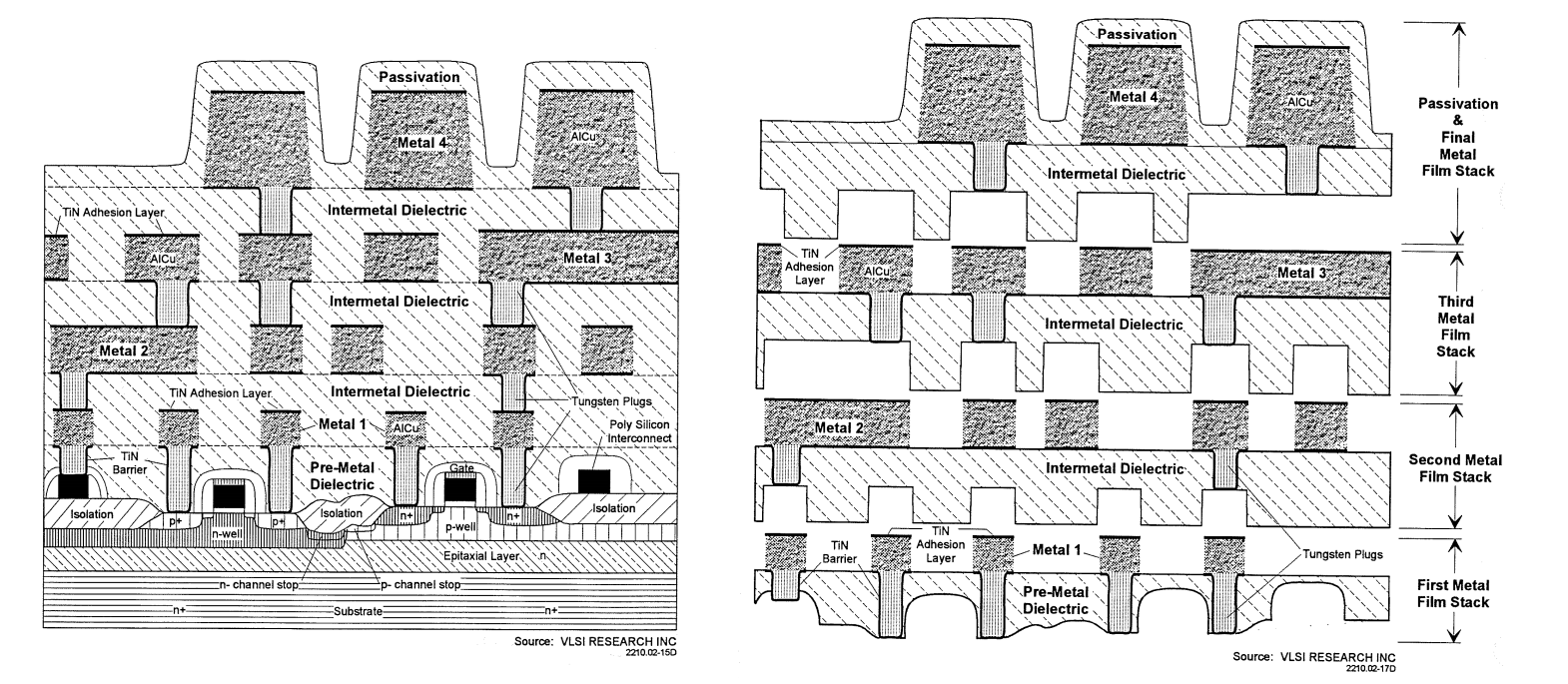

Cross-section of the target process with 10 planarized metal layers and... | Download Scientific Diagram

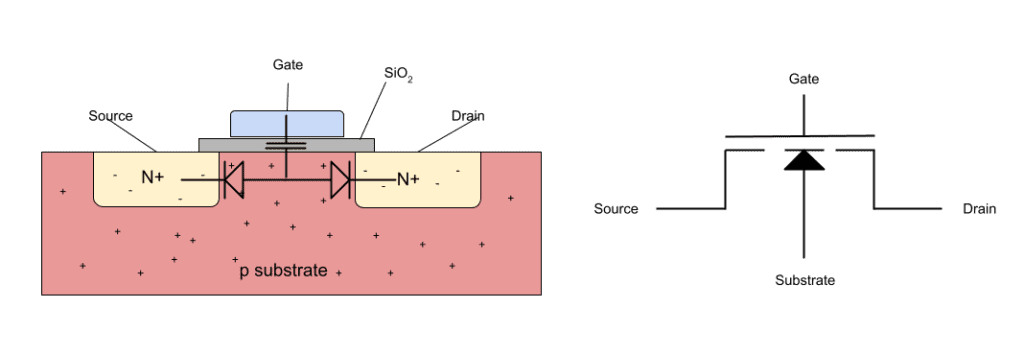

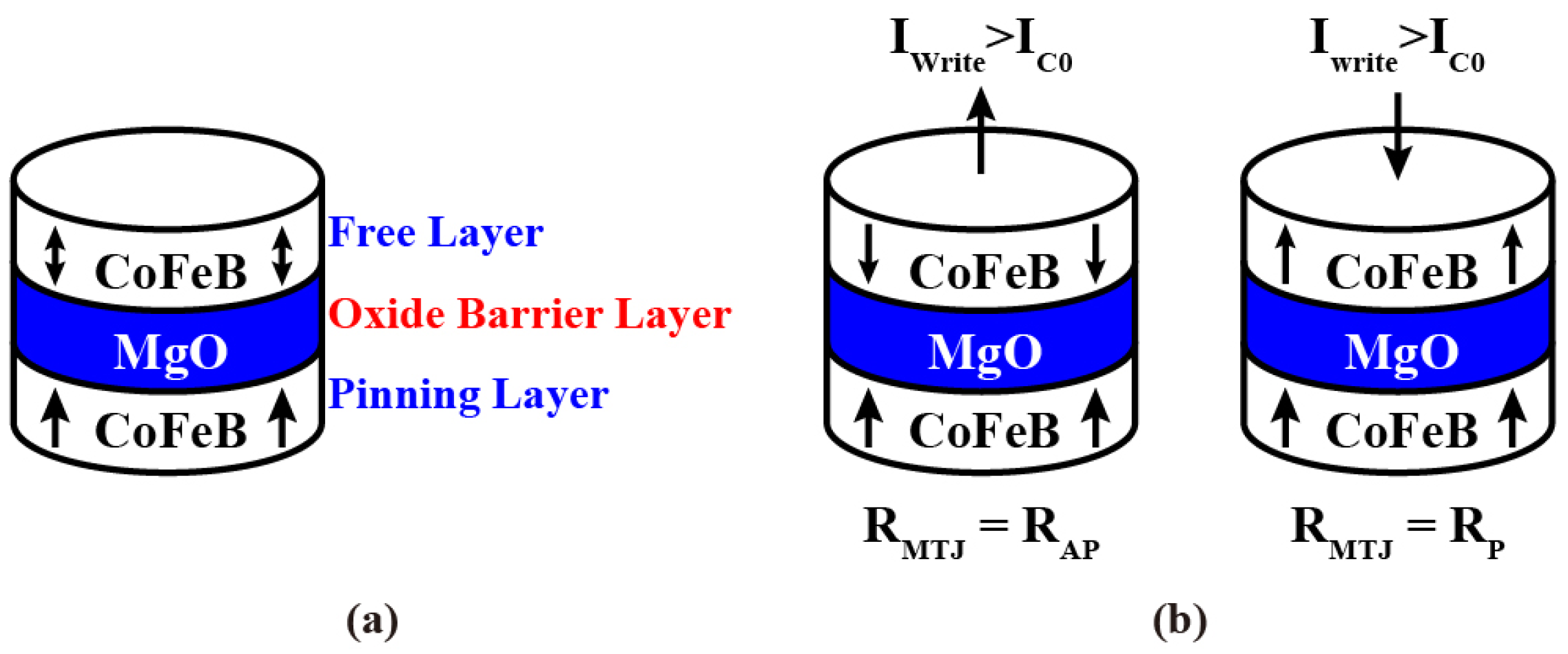

Electronics | Free Full-Text | A Reliability-Enhanced Differential Sensing Amplifier for Hybrid CMOS/MTJ Logic Circuits

InFO (Integrated Fan-Out) Wafer Level Packaging - Taiwan Semiconductor Manufacturing Company Limited

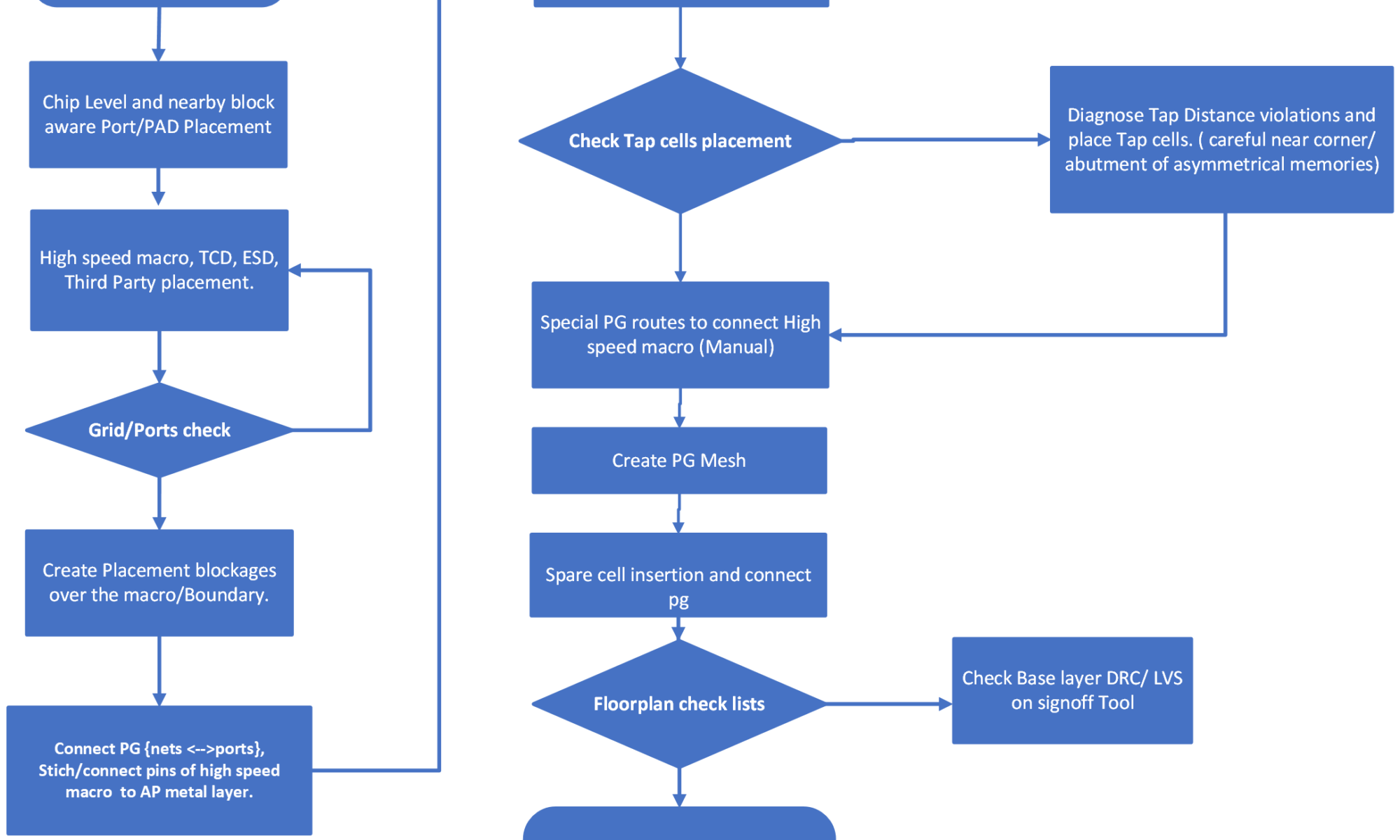

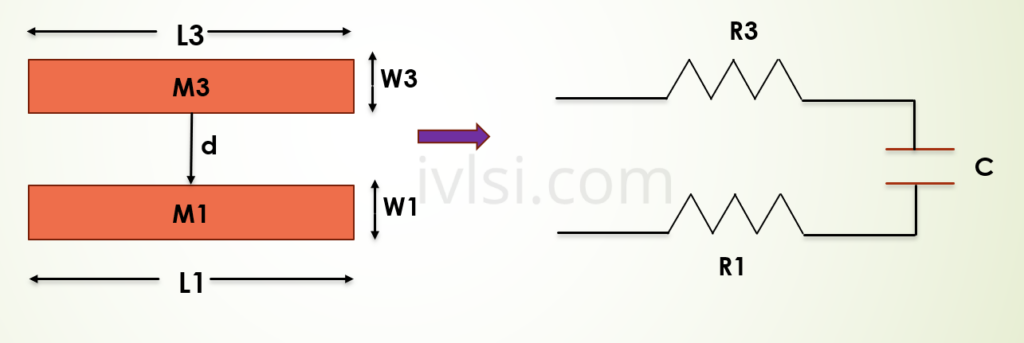

![PDF] Practical Routability-Driven Design Flow for Multilayer Power Networks Using Aluminum-Pad Layer | Semantic Scholar PDF] Practical Routability-Driven Design Flow for Multilayer Power Networks Using Aluminum-Pad Layer | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/15477a0896e29600ddf591b824dcc425e691839a/2-Figure1-1.png)

PDF] Practical Routability-Driven Design Flow for Multilayer Power Networks Using Aluminum-Pad Layer | Semantic Scholar

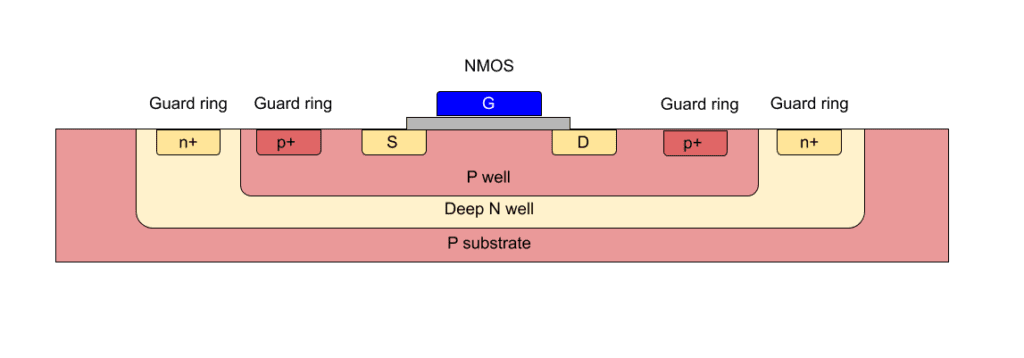

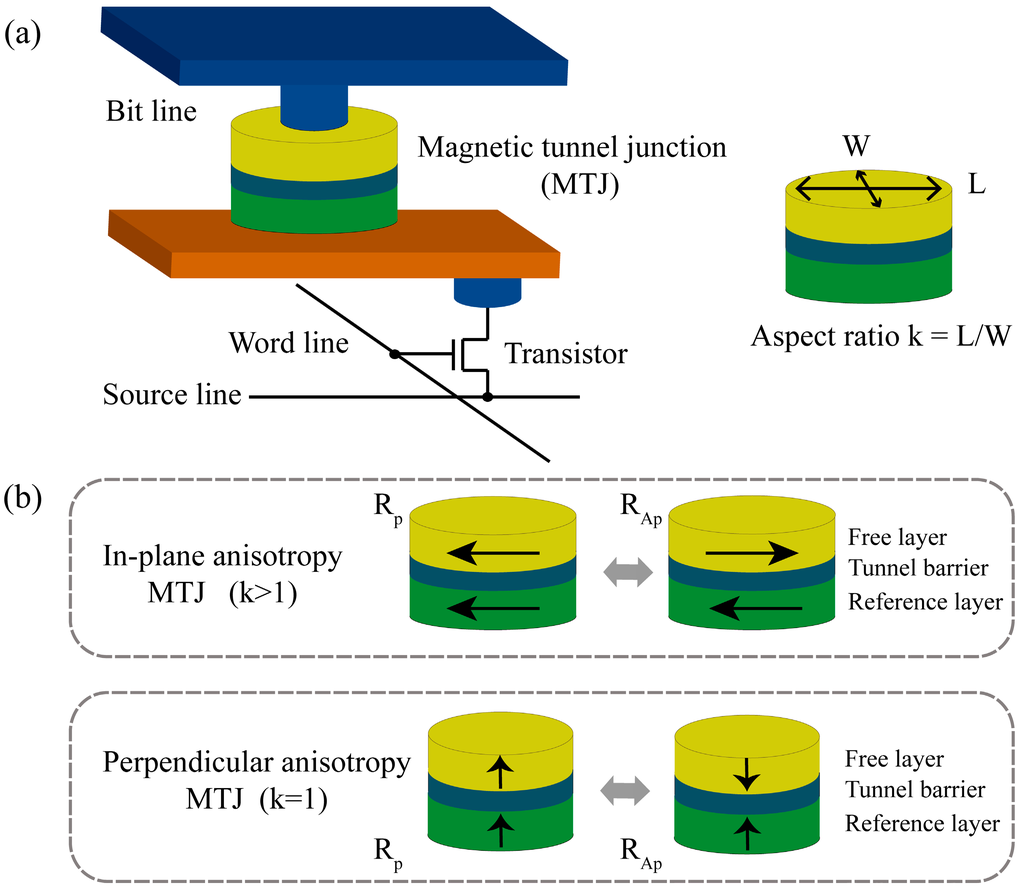

Micromachines | Free Full-Text | Tunnel Junction with Perpendicular Magnetic Anisotropy: Status and Challenges